Что такое чип: определение, классификация и процесс проектирования

Привет, ребята. Я Роуз. Сегодня я познакомлю вас с процессом проектирования чипов. Чипы, также известные как интегральные схемы или СБИС, представляют собой электронные схемы, состоящие из тысяч, миллионов или даже миллиардов транзисторов, резисторов и конденсаторов.

Темы, затронутые в этой статье: |

Ⅰ. Что такое чип? |

Ⅱ. Классификация чипов |

Ⅲ. Как устроен чип? |

Ⅰ. Что такое чип?

Чипы, также известные как интегральные схемы или СБИС, представляют собой электронные схемы, состоящие из тысяч, миллионов или даже миллиардов транзисторов, резисторов и конденсаторов. Она выполняет ту же задачу, что и более крупная схема, состоящая из дискретных (индивидуально упакованных) компонентов, но ИС представляет собой единое целое, построенное на небольшом куске полупроводникового материала. Поскольку кремний является наиболее распространенным сырьем, используемым для изготовления микросхем, их часто называют «кремниевыми чипами». Также можно использовать другое сырье, такое как германий и арсенид галлия, хотя кремний является предпочтительным вариантом по нескольким причинам:

Кремний является полупроводником, а это означает, что он может вести себя как проводник, так и изолятор в зависимости от условий легирования. Легирование — это процесс добавления примесей к элементу с целью повлиять на его электрические свойства.

Поскольку кремния на планете много, он довольно недорог.

Чипы — это специально созданные устройства, которые можно использовать в различных отраслях, включая аэрокосмическую, автомобильную, телекоммуникационную и компьютерную. В соответствии с требованиями приложения одна или несколько микросхем, других компонентов и разъемов размещаются на печатной плате (PCB) и соединяются тонкой медной лентой. Печатная плата часто используется в качестве материнской платы компьютера.

Ⅱ. Классификация чипов

Классификация распространенных микросхем, таких как ASIC , ASSP , SoC, FPGA , SoC FPGA, ucontroller, uprocessor и т. д., показана на схеме ниже.

Интегральная схема специального назначения (ASIC) — это аббревиатура от «Интегральная схема специального назначения». Это относится к ASIC, который представляет собой микросхему , разработанную для конкретного применения и используемую в электронном оборудовании, таком как маршрутизаторы, коммутаторы и модемы.

Основные особенности ASIC заключаются в следующем:

Выполнять одну и ту же функцию на протяжении всего жизненного цикла

Нет процессора

Цикл проектирования требует много времени и средств.

Массовое производство

Высокая скорость и низкое энергопотребление

Может быть цифровым, аналоговым или и тем, и другим.

ASSP или стандартные детали для определенных приложений — это микросхемы, разработанные для конкретных приложений, но не предназначенные для систем или клиентов. ASSP — это уникальный ASIC, который может использоваться различными компаниями. ASSP имеют те же функции, что и ASIC. Контроллеры Ethernet, контроллеры PCIE, интерфейсы USB и другие устройства используют его.

SoC (система на кристалле): SoC — это микросхема, объединяющая полную систему. Здесь расположены процессор, память, периферийные устройства и программное обеспечение. Микропроцессор (P или MPU), микроконтроллер (C или MCU ), процессор цифровых сигналов (DSP) или графический процессор — все это примеры процессоров SoC. Поскольку ASIC или ASSP с процессором представляет собой SoC, его свойства идентичны свойствам ASIC или ASSP. Обработка сигналов голоса, видео и изображения, беспроводная связь, автомобили и другие приложения.

FPGA (программируемая пользователем вентильная матрица): FPGA представляет собой программируемую интегральную схему. Он имеет программируемые межсоединения, настраиваемые логические блоки и настраиваемые блоки ввода-вывода. Обычно встречается в прототипах ASICS или SoC, контроллерах устройств, системах обработки сигналов и системах обработки изображений, а также в других приложениях. Ниже приведены основные характеристики FPGA:

Подходит для проектов, требующих частой настройки.

Нет процессора

Цикл проектирования не занимает много времени и не требует больших затрат.

Подходит для дизайна небольшого объема.

Низкая скорость и низкое энергопотребление

Программируемая SoC или SoC FPGA. Программируемая SoC или SoC FPGA представляет собой интегральную схему , которая сочетает в себе периферийные устройства, встроенную память, логические массивы в стиле FPGA и высокоскоростные приемопередатчики, а также архитектуру ЦП и FPGA. Обычно используется в сетевых, аэрокосмических и оборонных приложениях. Ниже приведены основные характеристики программируемой SoC/SoC FPGA:

Подходит для проектов, требующих частой настройки и возможностей обработки.

Меньший размер

Связь с более высокой пропускной способностью между процессором и FPGA

Цикл проектирования не занимает много времени и не требует больших затрат.

Низкий риск, поскольку его можно перепрограммировать.

Низкая скорость и низкое энергопотребление

Микропроцессор (μP или MPU): Микропроцессор — это интегральная схема, которая просто содержит ЦП . Он лишен какой-либо памяти (ОЗУ, ПЗУ и т. д.) или периферийных устройств. Микропроцессоры имеют следующие характеристики:

дорогой

Более высокая скорость и более высокое энергопотребление

Подходит для более крупных конструкций.

Выполняйте сложные задачи

Применение: настольные компьютеры, ноутбуки, блокноты, автомобили, поезда и т. д.

Микроконтроллер (μC или MCU): Микроконтроллер — это интегральная схема , содержащая процессор . память (ОЗУ, ПЗУ и т. д.) и различная периферия. Поскольку это устройство общего назначения, оно должно быть разработано специально для конкретного применения. Микроконтроллеры можно найти в широком спектре промышленных применений. SoC был уменьшен до микроконтроллера . Основные характеристики микроконтроллера следующие:

Компактный, поскольку все периферийные устройства находятся в микросхеме

Имеет процессор

Дешевле, чем микропроцессор .

Низкая скорость и низкое энергопотребление

Подходит для небольших конструкций, поскольку он компактен.

Выполняйте менее сложные задачи

Применение: микроволновые печи, стиральные машины, DVD-плееры, мобильные телефоны и т. д.

Ⅲ. Как устроен чип?

На следующем рисунке показан цикл проектирования микросхемы (каждый этап описан в следующем разделе):

Технические характеристики системы

Потенциальные клиенты встречаются с поставщиками микросхем, чтобы узнать, какие функции им нужны, и составить список необходимых функций. Процесс определения функциональных спецификаций (или требований) системы (ИС) и определения ее внешних интерфейсов известен как системная спецификация.

Архитектурный дизайн

После определения технических характеристик системы начинается процесс проектирования архитектуры системы. Это включает в себя определение программных интерфейсов, ограничений по времени, производительности, площади и мощности, а также разработку или приобретение блоков интеллектуальной собственности (IP). Поставщики IP могут предоставить стандартные промышленные IP-модули.

Проверка архитектуры

Процесс создания версии программного обеспечения аппаратной системы известен как проверка архитектуры. Для создания этого из функциональной модели используется язык высокого уровня (например, C, C++ или SystemC). Чтобы оценить архитектуру, производительность и мощность всей системы, используйте программный отладчик.

Формальная проверка/проверка атрибутов

Формальная проверка — это математический метод статического подтверждения правильности конструкции без использования каких-либо стимулирующих или временных тестов.

Чтобы установить, что реализованная модель системы соответствует критериям проектирования, используется формальный метод проверки, известный как проверка атрибутов (или спецификаций). Языки спецификации атрибутов (такие как PSL и SVA) используются для выражения системных требований и создания математической модели существующей системы при проверке атрибутов. Чтобы убедиться, что система соответствует критериям, используйте средство проверки модели для сравнения системных требований с математической моделью.

Ввод дизайна

Следующим шагом является ввод данных проекта, который происходит после проектирования и проверки архитектуры системы. Это процесс описания всей конструкции системы с помощью языка проектирования аппаратного обеспечения (HDL) (например, VHDL или Verilog) и/или построения схемы. Входные и выходные контакты I2C, образцы IP-блоков, конструктивные соединения, часы и методы сброса — все это подробно описано в проекте.

Функциональное моделирование

Процесс использования программного симулятора для проверки функционального поведения конструкции известен как функциональное моделирование. Это не учитывает временную задержку элемента дизайна. Он проверяет подключение на уровне IC, IP-блоки в среде уровня IC (которые обычно предварительно проверяются), сквозные функциональные маршруты, подключение контактной площадки, взаимодействие между модулями и взаимодействие внешних модулей.

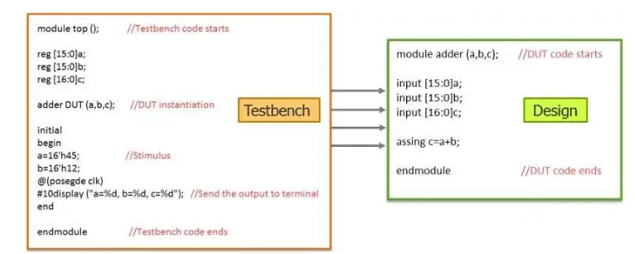

Тестовый стенд — это набор программ, используемых для определения того, соответствует ли реализация RTL стандартам проектирования (или нет). Он включает как действительные, так и ожидаемые, а также недопустимые и неожиданные условия, чтобы проверить, правильно ли работает конструкция.

Формальная проверка-проверка эквивалентности

Формальная проверка, как уже говорилось ранее, представляет собой средство статического подтверждения достоверности проекта с использованием математических методов, а не тестов на стимулы или время.

Проверка эквивалентности — это формальный метод проверки для определения функциональной эквивалентности проекта путем сравнения его с «золотым» проектом. Проверка эквивалентности на каждом этапе цикла проектирования ИС изображена на схеме ниже:

Предварительная проверка кремния

Практика оценки конструкции аппаратного обеспечения перед отправкой ее в производство известна как предварительная проверка кремния. Он может тестировать высокорискованную или вновь созданную интеллектуальную собственность без повторного запуска микросхемы, что позволяет сэкономить деньги. Предварительная проверка кристалла может выполняться с помощью симулятора или FPGA.

выгода:

Очень быстро по сравнению с моделируемой средой

Может обнаруживать ограниченный набор внутренних сигналов для отладки.

Сценарии на уровне программного обеспечения и приложений можно проверить перед записью на пленку.

предел:

Аппаратное обеспечение стоит дорого

Невозможно проверить имитируемую блокировку IP-адреса.

По сравнению с реальным чипом, тактовая частота системы медленнее

Требуется несколько настроек оборудования, особенно если группы проверки и программного обеспечения распределены в нескольких географических точках.

Моделирование

Процесс оценки системных функций на аппаратном устройстве, известном как эмулятор, называется эмуляцией. Симулятор может запускать очень большие проекты ИС намного быстрее, чем симуляция, и может одновременно запускать множество проектов ИС на разных тактовых частотах. Самый продвинутый тренажер изображен на схеме ниже:

Прототипирование на основе FPGA

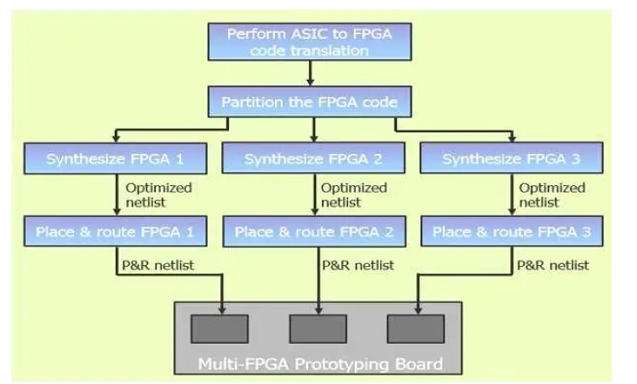

Метод проверки системных функций с использованием одной или нескольких FPGA известен как прототипирование на основе FPGA. Этапы прототипирования FPGA следующие:

Код уровня передачи регистров (RTL) из ASIC преобразуется в код RTL FPGA. Это влечет за собой, среди прочего, переключение между памятью, исключение аналоговых блоков и переписывание алгоритмов тактирования.

Если весь код RTL FPGA слишком велик для одной FPGA, он будет разделен на несколько FPGA.

Синтез, размещение и маршрут выполняются с помощью инструментов FPGA.

Проект проверяется после загрузки битового файла в FPGA.

Синтез

Учитывая ограничения технической библиотеки и дизайна, синтез — это процесс перевода предполагаемого кода RTL в оптимальное представление на уровне шлюза. При синтезе пройдите следующие этапы:

Код проектирования RTL преобразуется в логические уравнения, которые не зависят от технологии.

Булевы уравнения следует оптимизировать и удалить лишнюю логику.

Отображение технологий. Независимые от технологии логические уравнения сопоставляются с логическими элементами, связанными с технологией, с использованием проектных ограничений и технологических библиотек.

Статический временной анализ (STA)

Метод оценки временных характеристик проекта без каких-либо стимулов известен как статический временной анализ (STA). STA выполняется быстро и тщательно, но не проверяет функциональность проекта. Поскольку электронное оборудование управляется тактовым сигналом, необходимо обеспечить работу конструкции на заданной тактовой частоте. STA используется на каждом этапе процесса проектирования ИС.

Проектирование для испытаний (DFT)

Процесс создания интегральных схем не является безошибочным. В результате в проект должна быть включена дополнительная логика, известная как логика проектирования для тестирования (DFT), чтобы помочь в выявлении производственных дефектов во время постпроизводственного тестирования ИС. С использованием логики ДПФ микросхема сначала проверяется на наличие производственных дефектов. Проверьте работоспособность микросхемы на предмет отсутствия производственных дефектов.

Предварительное моделирование

Программное приложение оценивает функциональность и временные характеристики списка соединений уровня шлюза перед отправкой его в физическую структуру. Для этого используется предварительное моделирование.

Физическая планировка

Физическая компоновка — это переход между логическим и физическим представлениями ИС. Файл Graphic Database System (GDSII), который представляет собой двоичный формат файла, который кодирует плоские геометрические объекты, текстовые метки и другую информацию, связанную с физическим макетом, является результатом процесса физического макета. Ниже приведены этапы физического макета:

Определите основные блоки дизайна и распределите пространство в соответствии со стандартами времени, площади и производительности во время планирования компоновки. Здесь также определяются структура IP, соотношение сторон и параметры маршрутизации.

Разделение: Чтобы упростить планирование и маршрутизацию, разделите микросхему на функциональные блоки.

Размещайте и связывайте блоки дизайна таким образом, чтобы не противоречить стандартам проектирования.

Синтез дерева часов: часы равномерно распределяются по всем элементам синхронизации в проекте.

Моделирование после макетирования

После разработки физической компоновки конструкции для ее тестирования используется моделирование после компоновки. Ниже приведены проверки, выполняемые во время моделирования после компоновки:

Проверка правил проектирования (DRC): макет соответствует набору правил, необходимых для производства.

Проверка электрических правил (ERC). Планировка соответствует набору правил электрического проектирования.

Компоновка и схема (LVS): Компоновка функционально такая же, как спроектированный список соединений.

Производство интегральных схем

Список соединений компоновки отправляется производителю микросхемы в виде файла GDSII после моделирования после компоновки (литейное производство). Под выносом понимается процедура доставки документов GDSII на литейный завод. На следующей диаграмме показан процесс производства микросхемы:

тестер микросхем

Производство интегральных схем не является надежным на 100 процентов, что приводит к производственным дефектам во многих образцах. Тестер используется для фильтрации дефектных микросхем после их получения с литейного завода. Тестер подает на микросхему входной сигнал и проверяет выходной сигнал. Он также проверяет электрические и тепловые характеристики микросхемы и определяет оптимальные рабочие настройки.

Тестер микросхем

Посткремниевая проверка

Образцы, прошедшие испытание, подвергаются испытаниям в реальных условиях. Этот процесс известен как пост-кремниевая проверка. Используйте программный инструмент на компьютере, чтобы настроить микросхему и загрузить тестовый код на микросхему во время проверки после полупроводниковой схемы. Прогнозируемый результат отслеживается, и все функциональные возможности микросхемы проверяются. Настройки после проверки изображены на схеме ниже:

Обобщать

Существует множество различных типов интегральных схем, каждая из которых имеет свой набор функций: программируемые или непрограммируемые, с процессором или без него , высокоскоростные или низкоскоростные, компактные или громоздкие. Процесс разработки, производства и тестирования интегральных схем сложен и требует много времени. Ключевой вклад вносят группа проектирования и проверки, поставщики интеллектуальной собственности и производители микросхем. Усовершенствованные инструменты EDA имеют решающее значение для сокращения времени и усилий, необходимых для завершения цикла проектирования микросхем.

Frequently Asked Questions