Что такое ASIC-чип?

ASIC (интегральная схема специального назначения) — это интегральная схема специального назначения, которая представляет собой интегральную схему, разработанную и изготовленную в соответствии с конкретными требованиями пользователя и потребностями конкретной электронной системы.

Каталог |

Ⅰ Что такое чип ASIC? |

Ⅱ Процесс проектирования чипа ASIC |

Ⅲ Особенности чипа ASIC |

Ⅳ Классификация чипов ASIC |

Ⅴ Знакомство с продуктами ASIC-чипов |

Ⅰ Что такое чип ASIC?

Микросхема ASIC ( интегральная схема специального назначения ) представляет собой специализированную интегральную схему, запатентованную прикладную микросхему, разработанную и изготовленную на корневом уровне в ответ на требования пользователя к конкретной электронной системе, вычислительная мощность и вычислительная эффективность которой могут быть настроены в соответствии с потребностями алгоритма. и является продуктом оптимизированной конструкции с фиксированным алгоритмом. Чип-модули ASIC могут широко использоваться в устройствах искусственного интеллекта, устройствах для добычи виртуальной валюты, расходных печатных устройствах, устройствах военной обороны и других интеллектуальных терминалах.

На аппаратном уровне чипы ASIC состоят из основных кремниевых материалов, фосфида галлия, арсенида галлия, нитрида галлия и других материалов. На уровне физической структуры модули микросхем ASIC собираются из IP-ядер, таких как внешние устройства хранения данных, диспетчеры питания, процессоры аудиоэкранов и сетевые схемы. Один и тот же модуль микросхем может содержать одну или несколько микросхем ASIC с одинаковыми или разными функциями для удовлетворения одной или нескольких конкретных потребностей.

ASIC характеризуются требованиями, специфичными для пользователя, и имеют преимущества меньшего размера, меньшего энергопотребления, повышенной надежности, улучшенной производительности, повышенной конфиденциальности и более низкой стоимости по сравнению с ИС общего назначения, выпускаемыми в массовом производстве.

Интегральная схема — это миниатюрное электронное устройство или компонент. Используя определенный процесс, транзисторы, резисторы, конденсаторы и катушки индуктивности, необходимые в цепи и проводке, соединяются между собой, изготавливаются в виде одной или нескольких небольших полупроводниковых пластин или диэлектрических подложек, а затем упаковываются в оболочку, превращаясь в микроструктуру с требуемой функцией схемы. . Все компоненты конструкции составлены как единое целое, что обеспечивает миниатюризацию электронного компонента, низкое энергопотребление, интеллект и высокую надежность. Интегральные схемы были изобретены в 1970-х годах Джеком Килби (интегральные схемы на основе германия (Ge)) и Робертом Нойесом (интегральные схемы на основе кремния (Si)).

Чем больше масштаб интегральной схемы, тем сложнее создать систему, в которой будут меняться особые требования для решения этих проблем. Поэтому появление интегральных схем специального назначения (ASIC) с участием пользователя в проектировании позволяет добиться оптимального проектирования всей системы, превосходной производительности и конфиденциальности. ASIC могут объединять функции нескольких, десятков или даже сотен интегральных схем общего назначения среднего и малого масштаба на одном кристалле. И вся система может быть интегрирована на одном чипе для удовлетворения потребностей системы. Это делает всю схему оптимизированной. Уменьшилось количество компонентов, сократилась проводка, уменьшились объем и вес, повысилась надежность системы.

Ⅱ Процесс проектирования чипа ASIC

Во-первых, ASIC необходимо разделить на внутренние функциональные модули, чтобы каждый функциональный модуль реализовал соответствующую функцию. Каждый функциональный модуль соединен вместе, образуя всю схему ASIC. Во-вторых, логическое проектирование модулей выполняется на языке описания аппаратного обеспечения (HDL) для формирования кода уровня передачи регистров (RTL) в соответствии с функциональными и интерфейсными требованиями. В-третьих, в соответствии с функциональными и временными требованиями спецификации ASIC напишите тестовый код или тестовый стимул с использованием прототипа программируемой пользователем логической матрицы (FPGA) или программного моделирования, чтобы проверить логику и убедиться, что конструкция логики полностью соответствует проектным требованиям. В-четвертых, код RTL сопоставляется с соответствующей библиотекой процессов с помощью инструмента логического синтеза. Затем выполняются компоновка, проводка и другие макеты для завершения проверки сроков и согласования для формирования данных компоновки для производства штампов.

Ⅲ Особенности чипа ASIC

В отличие от обычных микросхем, таких как центральные процессоры, которые генерируют результаты путем чтения и выполнения инструкций внешнего программного кода, микросхемы ASIC считывают необработанные входные сигналы данных и генерируют выходные сигналы непосредственно после операций внутренней логической схемы.

1 Преимущества

По сравнению с процессорами, графическими процессорами , FPGA и другими типами чипов, чипы ASIC имеют множество преимуществ при применении специализированных систем, как показано в следующих аспектах.

① Преимущество площади: микросхемы ASIC разработаны таким образом, чтобы избежать избыточных логических блоков, блоков обработки, регистров, блоков хранения и других архитектур. Они построены в виде чисто цифровых логических схем, что позволяет уменьшить площадь кристалла. Чтобы справиться с чипами небольшой площади, можно вырезать большее количество чипов из пластины того же размера, что помогает компаниям снизить затраты на пластины.

② Преимущество энергопотребления: чипы ASIC потребляют меньше энергии на единицу арифметических операций по сравнению с ЦП, графическим процессором и FPGA, например, графический процессор потребляет около 0,4 Вт электроэнергии на единицу арифметических операций, а ASIC потребляет около 0,2 Вт электроэнергии на единицу арифметических операций. который может лучше соответствовать ограничениям энергопотребления новых умных бытовых приборов.

③ Преимущество интеграции: система микросхем ASIC, схема и процесс высоко интегрированы благодаря индивидуальному дизайну, что помогает клиентам получать высокопроизводительные интегральные схемы.

④ Ценовое преимущество: благодаря небольшому размеру, высокой скорости работы и низкому энергопотреблению чипы ASIC намного дешевле, чем чипы ЦП, графического процессора и FPGA. Текущая средняя цена чипов ASIC на мировом рынке составляет около 3 долларов. В долгосрочной перспективе, если будет достигнут масштаб массового производства, ожидается, что цена на чипы ASIC продолжит снижаться.

2 недостатка

① Микросхемы ASIC строго индивидуализированы, имеют длительные циклы проектирования и разработки, а готовые продукты должны пройти физическую конструкцию и проверку надежности.

② Чипы ASIC сильно зависят от алгоритмов. Алгоритмы искусственного интеллекта обновляются и повторяются с высокой скоростью, что приводит к высокой частоте обновления микросхем ASIC.

③ Высокая степень кастомизации чипов ASIC и относительно длительный цикл исследований и разработок увеличивают риск исключения готовой продукции ASIC с рынка.

Ⅳ Классификация чипов ASIC

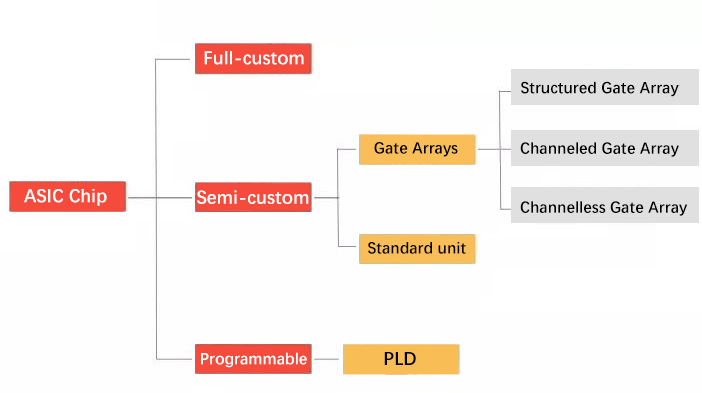

Классификация ASIC-чипов

(1) В зависимости от степени настройки

Чипы ASIC можно разделить на полностью специализированные микросхемы ASIC, полуиндивидуальные микросхемы ASIC и программируемые микросхемы ASIC.

① Полностью изготовленные на заказ чипы ASIC

Полностью настраиваемые микросхемы ASIC — это одни из самых настраиваемых микросхем, в которых разработчики проектируют логические блоки для различных функций на основе различных структур схем и создают на чипплате аналоговые схемы, блоки памяти и механические структуры. Логические ячейки соединены друг с другом с помощью плат масок, а платы масок микросхем ASIC также имеют широкие возможности настройки.

Разработка полностью специализированных микросхем ASIC обходится дорого: среднее время разработки каждого модуля микросхемы составляет более 9 недель. Этот тип чипа обычно используется для продвинутых приложений.

По сравнению с полукастомными чипами ASIC, полностью кастомные чипы ASIC превосходят их по производительности и энергопотреблению. Для той же функции средняя арифметическая производительность полностью специального ASIC-чипа примерно в 8 раз превышает среднюю арифметическую производительность полу-нестандартного ASIC-чипа при том же процессе, а производительность полностью специального ASIC-чипа с 24-нм техпроцессом лучше, чем у полукастомного чипа ASIC с 5-нм техпроцессом.

② Полуиндивидуальные ASIC-чипы

Большинство логических ячеек полузаказных ASIC взяты из стандартной библиотеки логических ячеек, а некоторые из них разработаны специально в соответствии с конкретными требованиями. Стоимость разработки ниже, а гибкость выше, чем у полностью специального ASIC-чипа.

В зависимости от количества стандартных логических ячеек и пользовательских логических ячеек полузаказные ASIC можно разделить на микросхемы вентильных матриц и микросхемы стандартных ячеек.

а. ASIC-чип массива ворот

Микросхема ASIC вентильной матрицы включает в себя канальную вентильную матрицу, бесканальную вентильную матрицу и структурированную вентильную матрицу. Структура чипа ASIC массива ворот на кремниевой пластине, заданное положение транзистора, не может быть изменена, разработчик в основном за счет изменения нижнего металлического слоя чипа и других способов настройки структуры межсоединения логического блока.

Микросхемы ASIC с каналированной вентильной матрицей : положения транзисторов в этих микросхемах строго фиксированы, и разработчики могут размещать схемы в заранее определенном пустом пространстве между рядами транзисторов.

Чип ASIC с каналированной вентильной матрицей

Бесканальные микросхемы ASIC с вентильной матрицей . В бесканальной структуре между рядами транзисторов нет пространства для компоновки схемы, и проектировщики обычно подключают провода над ячейками вентильной матрицы.

Бесканальная вентильная матрица ASIC

Микросхема ASIC со структурированной вентильной матрицей : эта структура состоит из основной строки вентильной матрицы и блока внедрения. Блок внедрения повышает гибкость схемы, но накладывает ограничения на размер микросхемы. При такой структуре площадь расположения линии используется более эффективно, стоимость проектирования снижается, а сроки выполнения работ сокращаются.

Микросхема ASIC со структурированной вентильной матрицей

б. Стандартный сотовый ASIC-чип

Этот тип микросхемы ASIC состоит из логических ячеек, выбранных из библиотеки стандартных ячеек. Разработчики могут расположить стандартные ячейки в соответствии с требованиями своего алгоритма. В дополнение к стандартным ячейкам в архитектуре микросхем ASIC стандартных ячеек также могут использоваться фиксированные блоки, такие как микроконтроллеры и микропроцессоры.

Стандартный сотовый ASIC-чип

③ Программируемый чип ASIC

Программируемые микросхемы ASIC можно разделить на микросхемы FPGA и микросхемы PLD. В реальном производстве число исследовательских институтов и компаний, которые классифицируют микросхемы FPGA как отличные от микросхем ASIC, увеличивается, поэтому в этом отчете PLD (программируемое логическое устройство) рассматривается только как подкатегория программируемых микросхем ASIC.

ПЛИС, также известные как программируемые логические устройства, включают в свою структуру матрицу базовых логических ячеек, триггеров, защелок и т.п., а их взаимосвязанные части существуют в виде отдельных модулей. Проектировщики могут программировать PLD для удовлетворения некоторых требований своих приложений.

(2) В соответствии с функцией терминала

Чипы ASIC можно классифицировать как чипы TPU, чипы BPU и чипы NPU в зависимости от функции терминала.

① TPU — это тензорные процессоры, предназначенные для машинного обучения. Например, в мае 2016 года Google разработала программируемый ускоритель искусственного интеллекта для платформы Tensorflow — программируемую педаль газа с искусственным интеллектом и внутренним набором инструкций, который запускается, когда программа Tensorflow меняет или обновляет свои алгоритмы.

② BPU — это мозговой процессор, архитектура встроенного процессора искусственного интеллекта, предложенная Horizon Technology.

③ NPU — это процессор нейронной сети, который имитирует человеческие нейроны и синапсы на уровне схемы и напрямую обрабатывает крупномасштабные данные электронных нейронов и синапсов с помощью набора инструкций глубокого обучения.

Ⅴ Знакомство с продуктами ASIC-чипов

① Google выпустила TPU в 2016 году, а версия физического процессора AlphaGo от Google 2017 года оснащена четырьмя TPU, которые могут поддерживать платформу Google Cloud TPU и суперкомпьютер с машинным обучением.

② В августе 2014 года IBM выпустила чип TrueNorth второго поколения с 28-нм техпроцессом, моделирующий структуру мозга, который можно применять для обработки видео в реальном времени.

③ Intel представила семейство микросхем ASIC Xeon в 2017 году. Эта серия микросхем может работать как автономный процессор без необходимости использования дополнительных хост-процессоров и вспомогательных процессоров, а также может применяться для машинного глубокого обучения.

④ Стэнфордский университет представил чипы ASIC на основе новой нейроморфной вычислительной архитектуры со скоростью вычислений в 9000 раз выше, чем у обычного компьютера, которые могут моделировать около 1 миллиона нейронов головного мозга и миллиарды синаптических связей.

⑤ Развивающиеся научно-технические компании расширяют применение чипов ASIC в сфере безопасности, помощи при вождении, традиционной бытовой технике, интеллектуальной медицине и других областях.

Frequently Asked Questions