Введение в корпус микросхем

В последние годы появились технологии упаковки микросхем и появились новые термины. Можно перечислить как минимум несколько десятков названий, связанных с корпусами микросхем.

Каталог | |

Упаковка ИС на основе расширения плоскости XY

| ФОУЛП |

ИНФОРМАЦИЯ | |

ФОПЛП | |

ЕМИБ | |

Корпус ИС на основе расширения оси Z

| КоВос |

ХБМ | |

HMC | |

Широкий ввод-вывод | |

Фоверос | |

Ко-EMIB (Foveros + EMIB) | |

SoIC | |

X-куб | |

Краткое содержание | |

Мы разделяем упаковку ИС на две основные категории: (i) технологии упаковки ИС, основанные на расширении плоскости XY, которые в основном расширяют и соединяют сигналы через RDL; и (ii) технологии упаковки ИС, основанные на расширении оси Z, которые в основном расширяют и соединяют сигналы через TSV.

Упаковка ИС на основе расширения плоскости XY

Плоскость XY здесь относится к плоскости XY пластины или чипа. Отличительной особенностью этого типа корпуса является отсутствие кремниевых переходных отверстий TSV, а средства или технология расширения сигнала в основном реализуются через слои RDL, обычно без подложки. Проводка RDL крепится к кремниевому корпусу чипа или к дополнительному молдингу. Поскольку конечная упаковка не имеет подложки, эти упаковки относительно тонкие и сейчас широко используются в смартфонах.

ФОУЛП

FOWLP (Пакет уровня пластины с разветвленным выходом) — это разновидность WLP (Пакет уровня пластины), поэтому нам нужно сначала понять пакет уровня пластины WLP.

До появления технологии WLP традиционный процесс упаковки в основном осуществлялся после нарезания кубиками голых пластин, при этом пластины сначала нарезались кубиками, а затем упаковывались в различные формы.

WLP был представлен примерно в 2000 году и существует двух типов: с разветвлением и с разветвлением.

После завершения упаковки вафлю разрезают и нарезают ломтиками. Размер упакованного чипа почти такой же, как и у голого чипа, поэтому его также называют CSP (Chip Scale Package) или WLCSP (Wafer Level Chip Scale Packaging). Эти упаковки соответствуют рыночным тенденциям легкой, маленькой, короткой и тонкой бытовой электроники.

Вначале WLP в основном имели форму Fan-in, которую можно назвать Fan-in WLP или FIWLP, и в основном использовались для микросхем с небольшой площадью и малым количеством контактов.

С усовершенствованием процесса изготовления ИС площадь чипа уменьшается, и на ней не может разместиться достаточное количество контактов. Поэтому форма корпуса Fan-Out WLP, также известная как FOWLP, была разработана для полного использования RDL за пределами области микросхемы для создания соединений для большего количества контактов.

Порядок работы пакета FOWLP показан на рисунке ниже.

Процесс упаковки FOWLP

ИНФОРМАЦИЯ

InFO (Integrated Fan-out) — это технология упаковки микросхем FOWLP, разработанная TSMC в 2017 году. Это интеграция процесса FOWLP, которую можно понимать как интеграцию процесса разветвления нескольких микросхем, в то время как FOWLP предпочитает разветвление. сам процесс упаковки.

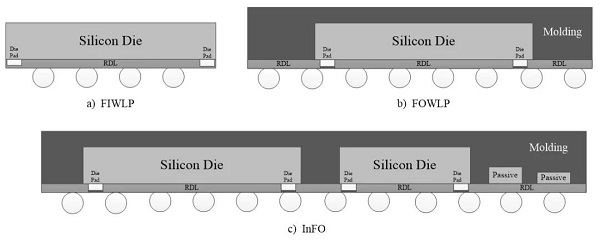

InFO дает возможность для интеграции нескольких чипов и может применяться для упаковки радиочастотных и беспроводных чипов, корпусов процессоров и чипов основной полосы частот, а также корпусов графических процессоров и сетевых чипов. На следующей диаграмме показано сравнение FIWLP, FOWLP и InFO.

Сравнительная схема FIWLP, FOWLP и InFO

Процессоры Apple iPhone в первые годы производились компанией Samsung, но TSMC из Apple A11 начала принимать заказы на процессоры двух поколений iPhone. Один из ключей заключается в новой технологии упаковки InFO от TSMC, которая обеспечивает прямое соединение между чипами, уменьшая толщину и освобождая ценное пространство для батарей или других деталей.

Apple начала использовать упаковку InFO с iPhone 7 и продолжает использовать ее впоследствии. iPhone 8 и iPhone X, включая мобильные телефоны других марок в будущем, также начнут использовать эту технологию в целом. Присоединение Apple и TSMC изменило статус применения технологии FOWLP и позволит рынку начать постепенно принимать и широко применять технологию упаковки FOWLP (InFO).

ФОПЛП

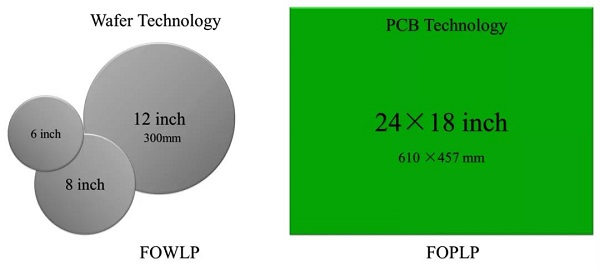

FOPLP (Пакет уровня разветвленной панели) основан на идее и технологии FOWLP, но использует панель большего размера, поэтому его можно массово производить в корпусе, в несколько раз превышающем размер кремниевой пластины 300 мм.

Технология FOPLP является расширением технологии FOWLP, которая представляет собой процесс разветвления на более крупной квадратной несущей плате, отсюда и название технологии упаковки FOPLP.

В настоящее время FOPLP использует несущую плату печатной платы размером 24 × 18 дюймов (610 × 457 мм), что примерно в четыре раза превышает площадь кремниевой пластины диаметром 300 мм. Следовательно, можно просто считать, что за один процесс можно массово производить в 4 раза больше корпусов микросхем, чем кремниевых пластин диаметром 300 мм.

Как и процесс FOWLP, технология FOPLP может объединить переднюю и заднюю стадии процесса упаковки и может рассматриваться как единый процесс упаковки, что значительно снижает производственные и материальные затраты. На рисунке ниже показано сравнение FOWLP и FOPLP.

Сравнение FOWLP и FOPLP

FOPLP использует технологию производства печатных плат для производства RDL, ширина и шаг линий в настоящее время превышают 10 мкм, а оборудование SMT используется для размещения чипов и пассивных устройств. Поскольку площадь панели намного больше площади пластины, он может упаковывать больше продуктов за один раз. По сравнению с FOWLP, FOPLP имеет большие преимущества в стоимости. В настоящее время крупнейшие мировые компании по производству упаковки, в том числе Samsung Electronics и Sun and Moon, активно участвуют в технологии FOPLP.

ЕМИБ

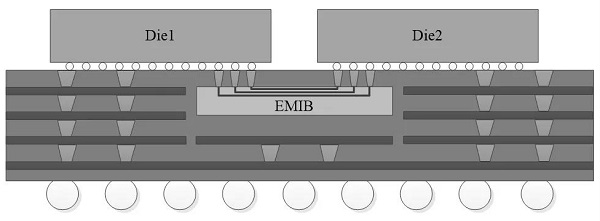

EMIB (Embedded Multi-Die Interconnect Bridge) — технология упаковки микросхем встроенного многочипового межкомпонентного моста, предложенная Intel и активно применяемая. В отличие от трех типов корпусов микросхем, описанных ранее, EMIB представляет собой корпус класса подложки. Поскольку EMIB также не имеет TSV, он также классифицируется как технология упаковки ИС, основанная на расширении плоскости XY.

Концепция EMIB аналогична 2.5D-корпусу, основанному на кремниевом промежуточном слое, который представляет собой локализованное соединение высокой плотности через кремниевую пластину. По сравнению с традиционными упаковками 2,5 технология EMIB имеет преимущества: нормальный выход упаковки, отсутствие дополнительных процессов и простота конструкции из-за отсутствия TSV.

При использовании традиционных чипов SoC ЦП, графический процессор, контроллер памяти и контроллер ввода-вывода могут быть изготовлены с использованием только одного процесса. Благодаря технологии EMIB процессор и графический процессор могут использовать 10-нм процесс, блок ввода-вывода и блок связи могут использовать 14-нм процесс, а часть памяти может использовать 22-нм процесс. Используя технологию упаковки EMIBIC, три различных процесса могут быть интегрированы в один процессор. На диаграмме ниже показана диаграмма EMIB.

ЕМИБ

По сравнению с кремниевым переходником, область кремния EMIB меньше и более гибкая. Технология упаковки EMIB позволяет при необходимости упаковывать вместе процессоры, устройства ввода-вывода, графические процессоры и даже FPGA, AI и другие микросхемы. И он может объединять чипы 10-нм, 14-нм, 22-нм и других различных процессов в один чип, чтобы адаптироваться к потребностям гибкого бизнеса.

Благодаря подходу EMIB платформа KBL-G объединяет процессоры Intel Core с графическими процессорами AMD Radeon RX Vega M, обеспечивая как мощные вычислительные возможности процессоров Intel, так и выдающиеся графические возможности графических процессоров AMD. Этот чип вошел в историю и вывел качество продукта на новый уровень.

Корпус ИС на основе расширения оси Z

Технология упаковки ИС на основе расширения оси Z в основном используется для расширения сигнала и соединения через TSV, который можно разделить на 2,5D TSV и 3D TSV, с помощью которых несколько микросхем могут быть вертикально сложены и соединены между собой.

В технологии 3D TSV чипы расположены близко друг к другу, поэтому задержка будет меньше. Кроме того, более короткая длина межсоединения снижает связанные с этим паразитные эффекты и позволяет устройству работать на более высокой частоте, что приводит к повышению производительности и снижению затрат.

Технология TSV является ключевой технологией для 3D-упаковки, и исследовательские организации, в том числе производители полупроводниковой интеграции, литейные предприятия по производству микросхем, фабрики по производству корпусов, разработчики новых технологий, университеты и исследовательские институты, а также технологические консорциумы, разработали множество аспектов процесса TSV.

Хотя технология упаковки ИС на основе расширения оси Z в основном используется для расширения сигнала и соединения через TSV, RDL также незаменим, например, если TSV верхнего и нижнего слоев микросхемы не могут быть выровнены, локальное соединение через RDL необходимый.

КоВос

CoWoS (Chip-on-Wafer-on-Substrate) — это технология упаковки 2.5D TSMC, которая упаковывает чип в кремниевый переходник (промежуточный слой) и соединяет его с помощью проводов высокой плотности на кремниевом переходнике перед установкой его на подложку корпуса. как показано на рисунке ниже.

КоВос

CoWoS и InFO — оба от TSMC, CoWoS имеет Silicon Interposer, а InFO — нет. CoWoS предназначен для рынка высокого класса, количество проводов и размер корпуса больше. InFO предназначен для экономичного рынка, размер упаковки меньше, а количество проводов меньше.

TSMC начала массовое производство CoWoS в 2012 году, объединяя несколько чипов вместе с помощью этой технологии. Благодаря межсоединению высокой плотности Silicon Interposer достигается небольшой размер корпуса, высокая производительность, низкое энергопотребление и меньшее количество контактов.

Технология CoWoS широко используется: GP100 от Nvidia, чип Google TPU2.0, лежащий в основе AlphaGo, который победил Кэ Цзе, — все они используют технологию CoWoS. Искусственный интеллект ИИ также является вкладом CoWoS. В настоящее время CoWoS поддерживается производителями высокопроизводительных чипов, такими как NVIDIA, AMD, Google, XilinX и Huawei.

ХБМ

ХБМ(High-Bandwidth Memory) — это память с высокой пропускной способностью, предназначенная для рынка высококачественной графики. HBM использует технологии 3D TSV и 2.5D TSV для объединения нескольких микросхем памяти в 3D TSV, а также технологию 2.5D TSV для соединения сложенных микросхем памяти с графическим процессором на несущей плате. На диаграмме ниже показана схема технологии HBM.

HBM (память с высокой пропускной способностью)

HBM в настоящее время доступен в трех версиях: HBM, HBM2 и HBM2E, с пропускной способностью 128 ГБ/с/стек, 256 ГБ/с/стек и 307 Гбит/с/стек соответственно, причем последняя версия HBM3 все еще находится в разработке.

AMD, NVIDIA и Hynix продвигают стандарт HBM: AMD сначала использовала его для своих флагманских видеокарт с пропускной способностью памяти до 512 Гбит/с, а NVIDIA следует этому примеру, используя HBM для достижения пропускной способности памяти 1 ТБ/с. По сравнению с DDR5 HBM повышает производительность более чем в 3 раза, но снижает энергопотребление на 50%.

HMC

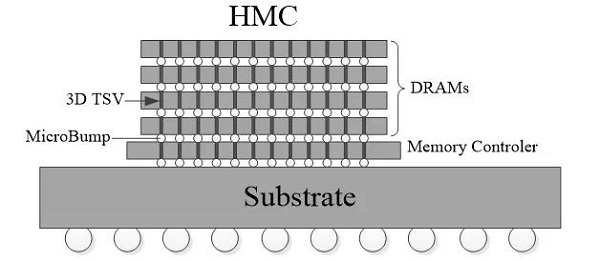

HMC (Hybrid Memory Cube) — это гибридный куб памяти, стандарт которого продвигает Micron. Ее целевым рынком является рынок высокопроизводительных серверов, особенно для многопроцессорных архитектур. HMC использует составные микросхемы DRAM для достижения большей пропускной способности памяти. Кроме того, HMC интегрирует контроллер памяти в составной пакет DRAM с помощью технологии интеграции 3D TSV. На диаграмме ниже показана технология HMC.

HMC

Разница между HBM и HMC заключается в том, что HBM соединен с графическим процессором через Interposer, тогда как HMC монтируется непосредственно на подложке, без Interposer и 2.5D TSV.

В стеке HMC 3D TSV имеют диаметр около 5–6 мкм и насчитывают более 2000+. Чипы DRAM обычно утончаются до 50 мкм и соединяются друг с другом через MicroBump толщиной 20 мкм.

Раньше контроллеры памяти изготавливались внутри процессора, поэтому в высокопроизводительных серверах, когда требуется большое количество модулей памяти, конструкция контроллеров памяти очень сложна. Теперь, когда контроллер памяти интегрирован в модуль памяти, конструкция контроллера памяти значительно упрощается. Кроме того, HMC использует высокоскоростной последовательный интерфейс (SerDes) для реализации высокоскоростного интерфейса, который подходит для ситуаций, когда процессор и память находятся далеко друг от друга.

Широкий ввод-вывод

Wide-IO (Wide Input Output) — это технология, продвигаемая Samsung и в настоящее время находящаяся во втором поколении, обеспечивающая разрядность интерфейса памяти до 512 бит, рабочую частоту интерфейса памяти до 1 ГГц и общую пропускную способность памяти до 68 ГБ/с. , что вдвое превышает пропускную способность интерфейсов DDR4 (34 ГБ/с).

Широкий ввод-вывод реализуется путем установки микросхем памяти на микросхемы логики, а микросхемы памяти подключаются к микросхемам логики и подложке через 3D TSV, как показано на рисунке ниже.

Широкий ввод-вывод

Благодаря преимуществам вертикального стекового пакета архитектуры TSV Wide-IO помогает создавать мобильную память с характеристиками скорости, емкости и мощности, отвечающими потребностям мобильных устройств, таких как смартфоны, планшеты и портативные игровые консоли. Основной целевой рынок — мобильные устройства, требующие низкого энергопотребления.

Фоверос

В дополнение к представленному ранее пакету EMIBIC, Intel также представила активную встроенную технологию Foveros. В представлении технологии Intel Foveros называется 3D Face to Face Chip Stack для гетерогенной интеграции, трехмерный стек микросхем для гетерогенной интеграции лицом к лицу.

Разница между EMIB и Foveros заключается в том, что первая представляет собой технологию 2D-упаковки, а вторая — технологию 3D-штабелирования. По сравнению с методом упаковки 2D EMIB, Foveros больше подходит для продуктов малого форм-фактора или продуктов с более высокими требованиями к пропускной способности памяти. На самом деле различия между EMIB и Foveros с точки зрения производительности и функциональности чипов не значительны, поскольку оба представляют собой чипы с разными характеристиками и функциями, интегрированные вместе для выполнения разных ролей. Однако с точки зрения объема, энергопотребления и т. д. проявляются преимущества стекирования Foveros 3D.

На следующем рисунке показана схема технологии упаковки Foveros 3D.

Фоверос

Ко-EMIB (Foveros + EMIB)

Co-EMIB представляет собой комбинацию EMIB и Foveros. EMIB в основном отвечает за горизонтальное соединение, позволяя собирать микросхемы с разными ядрами, как пазл. Фоверос, с другой стороны, представляет собой вертикальную конструкцию, подобную высотному зданию, где каждый этаж может иметь совершенно разный дизайн, например, тренажерный зал на втором этаже, офисное здание на втором этаже и квартира на втором. третий этаж.

Технология упаковки, сочетающая в себе EMIB и Foveros, называется Co-EMIB и представляет собой метод изготовления чипов, который может обладать большей гибкостью, позволяя продолжать сшивать чипы горизонтально во время их укладки. Таким образом, эта технология позволяет объединять несколько чипов 3D Foveros вместе с помощью EMIB для создания более крупных систем микросхем. На диаграмме ниже показана схема технологии Co-EMIB.

Со-EMIB (Foveros + EMIB)

Технология упаковки Co-EMIB может обеспечить производительность, сравнимую с производительностью одного чипа. Ключом к достижению этой технологии является ODI (всенаправленное межсоединение), которое имеет два разных типа соединений: не только соединения лифтового типа с разными уровнями, но также мосты к различным трехмерным структурам и мезонинные слои между слоями, что позволяет использовать разные чипы. комбинации, обеспечивающие высокую гибкость. Технология упаковки ODI позволяет соединять чипы как горизонтально, так и вертикально.

Co-EMIB, благодаря новому подходу к упаковке 3D + 2D, также превращает мышление в проектировании микросхем из плоской головоломки прошлого в штабелирование блоков. Таким образом, в дополнение к новым революционным вычислительным архитектурам, таким как квантовые вычисления, CO-EMIB — лучший способ сохранить и продолжить существующую вычислительную архитектуру и экологию.

SoIC

SoIC, также известная как TSMC-SoIC, представляет собой новую технологию, предложенную TSMC — систему на интегрированных кристаллах (SoIC).

SoIC — это инновационная технология многокристального стека, которая обеспечивает интеграцию процессов менее 10 нм на уровне пластин. Наиболее отличительной особенностью этой технологии является структура соединения без выступов, что приводит к более высокой плотности интеграции и лучшим эксплуатационным характеристикам.

SoIC содержит два типа технологических форм: CoW (чип на пластине) и WoW (вафля на пластине), из описания TSMC SoIC представляет собой прямое соединение пластины с пластиной WoW или чипа с пластиной CoW (Bonding). ) технология, которая относится к технологии Front-End 3D (FE 3D), при этом важнейшими технологиями являются вышеупомянутые InFO и CoWoS. TSMC и Siemens EDA (Mentor) сотрудничали в области технологии SoIC и представили соответствующие инструменты проектирования и проверки.

На рисунке ниже показано сравнение интеграции 3D IC и SoIC.

Сравнение интеграции 3D IC и SoIC

В частности, процесс создания SoIC и 3D IC в чем-то похож. Ключом к созданию SoIC является создание структуры соединения без неровностей, а плотность TSV у него также выше, чем у традиционных 3D-ИС, которые напрямую соединяют несколько слоев микросхем через очень маленькие TSV. На рисунке выше показано сравнение плотности TSV и размера Bump между 3D-микросхемами и SoIC. Видно, что плотность TSV SoIC намного выше, чем у 3D IC, а соединение между чипами также осуществляется с помощью технологии прямого соединения без Bump, что приводит к меньшему шагу чипа и более высокой плотности интеграции, и, следовательно, к его продуктам. имеют более высокую функциональную плотность, чем традиционные 3D-ИС.

X-куб

X-Cube (eXtended-Cube) — это технология 3D-интеграции, анонсированная компанией Samsung, позволяющая разместить больше памяти в меньшем пространстве и уменьшить расстояние сигнала между ячейками.

X-Cube используется в процессах, требующих высокой производительности и пропускной способности, таких как 5G, искусственный интеллект, носимые или мобильные устройства, а также в приложениях, требующих высокой вычислительной мощности. В x-Cube используется технология TSV для размещения SRAM поверх логической ячейки, что позволяет разместить больше памяти в меньшем пространстве.

X-куб

Как видно на демонстрационной диаграмме технологии X-Cube, в отличие от предыдущих параллельных 2D-пакетов из нескольких микросхем, пакет X-Cube 3D позволяет штабелировать и упаковывать несколько микросхем, что приводит к более компактной готовой структуре чипа. Технология TSV используется для соединения чипов друг с другом, снижая энергопотребление и одновременно увеличивая скорость передачи. Эта технология будет использоваться в передовых технологиях 5G, AI, AR, HPC, мобильных чипах и виртуальной реальности.

Технология X-Cube резко сокращает расстояние передачи сигнала между чипами, увеличивает скорость передачи данных, снижает энергопотребление, а также позволяет настраивать пропускную способность и плотность памяти в соответствии с потребностями заказчика. В настоящее время технология X-Cube уже поддерживает 7-нм и 5-нм процессы, и Samsung продолжит работать с мировыми полупроводниковыми компаниями над внедрением этой технологии в высокопроизводительные чипы следующего поколения.

Краткое содержание

В этой статье мы описали 12 наиболее распространенных передовых технологий упаковки микросхем , доступных сегодня. В следующей таблице представлено параллельное сравнение этих основных технологий упаковки микросхем.

Горизонтальное сравнение основных передовых упаковочных технологий

Из сравнения мы видим, что появление и быстрое развитие современной упаковки произошло в основном за последние 10 лет, ее технология интеграции в основном включает в себя 2D, 2,5D, 3D, 3D+2D, 3D+2,5D нескольких типов, функциональная плотность также низкий, средний, высокий, очень высокий несколько, области применения включают 5G, искусственный интеллект, носимые устройства, мобильные устройства, высокопроизводительные серверы, высокопроизводительные вычисления, высокопроизводительные видеокарты. Основные производители приложений включают TSMC, Intel, SAMSUNG и другие известные производители чипов, что также отражает тенденцию интеграции упаковки микросхем и производства чипов.

Наконец, подведем итог: цель усовершенствованной упаковки состоит в том, чтобы:

Улучшите функциональную плотность, сократите длину межсоединений, улучшите производительность системы и уменьшите общее энергопотребление.

Frequently Asked Questions