Что такое CPLD (сложное программируемое логическое устройство)?

CPLD использует технологии программирования CMOS EPROM, EEPROM, флэш-памяти и SRAM, образуя таким образом программируемое логическое устройство с высокой плотностью, высокой скоростью и низким энергопотреблением. Они относительно велики по размеру и сложны по структуре и относятся к классу больших интегральных схем.

Каталог |

Ⅰ Знакомство с устройством |

Ⅱ Состав CPLD |

Ⅲ Структура CPLD |

Ⅳ Идентификация и классификация FPGA и CPLD. |

Ⅰ Знакомство с устройством

CPLD ( комплексное программируемое логическое устройство ) в основном состоит из программируемых логических макроячеек (MC), расположенных вокруг центра ячейки программируемой матрицы межсоединений. Среди них структура MC является более сложной и имеет сложную структуру соединения ячеек ввода-вывода, которая может быть создана пользователем в соответствии с потребностями конкретной структуры схемы для выполнения определенных функций. Поскольку CPLD использует металлические провода фиксированной длины для внутреннего соединения каждого логического блока, разработанные логические схемы предсказуемы во времени, что позволяет избежать недостатка, заключающегося в том, что время сегментированной структуры межсоединений не полностью предсказуемо.

История развития

В 1970-х годах появилось самое раннее программируемое логическое устройство — PLD. Его выходная структура представляла собой программируемые логические макроячейки. Поскольку проектирование его аппаратной структуры могло быть выполнено с помощью программного обеспечения, его конструкция была очень гибкой, чем у чисто аппаратных цифровых схем. Но из-за слишком простой структуры они также позволяли реализовывать только небольшие схемы. Чтобы компенсировать этот недостаток, заключающийся в том, что PLD могут проектировать только небольшие схемы, в середине 1980-х годов были представлены сложные программируемые логические устройства — CPLD .

Особенности устройства

CPLD обладает такими характеристиками, как гибкое программирование, высокая степень интеграции, короткий цикл проектирования и разработки, широкая применимость, передовые инструменты разработки, низкие затраты на проектирование и производство, низкие требования к опыту работы с оборудованием для дизайнеров, отсутствие необходимости тестирования для стандартных продуктов, высокая конфиденциальность и доступная цена. и т. д. Он может реализовать крупномасштабное проектирование схем, поэтому он широко используется при создании прототипов продуктов и производстве продуктов (обычно менее 10 000 штук). Устройства CPLD стали неотъемлемой частью электронных продуктов, а их проектирование и применение стали необходимым навыком для инженеров-электронщиков.

Как использовать CPLD?

CPLD — это своего рода цифровая интегральная схема , в которой пользователи создают свои собственные логические функции в соответствии со своими потребностями. Основной метод проектирования заключается в использовании интегрированной программной платформы разработки для создания соответствующего целевого файла с использованием принципиальной схемы и языка описания аппаратного обеспечения, а затем передачи кода на целевой чип через кабель загрузки («внутрисистемное» программирование) для реализации разработана цифровая система.

Вот в качестве примера процесс проектирования (декорирования) схватчика, т.е. поток проектирования чипа. большая часть работы CPLD выполняется на компьютере. Откройте интегрированное программное обеспечение для разработки (Altera Max+pluxII) → нарисуйте принципиальную схему, напишите язык описания оборудования (VHDL, Verilog) → скомпилируйте → подайте входной сигнал возбуждения логической схемы, смоделируйте и проверьте правильность результата логического вывода. → выполнить блокировку ввода и вывода контактов (64 входных и выходных контакта 7128 можно установить по мере необходимости) → сгенерировать код → передать и сохранить код в чипе CPLD через кабель загрузки.

Введено 7128 выводов микросхемы. Цифровая трубка, викторина, индикатор, зуммер через провод к ДСП.

Схема системного интерфейса с использованием чипа CPLD, а затем включите питание для теста. При нажатии переключателя викторины должен загореться индикатор соответствующего бита. После того, как ответ будет правильным, рефери прибавит баллы, чтобы проверить, правильно ли в данный момент отображается цифровое табло. Если вы обнаружите какую-либо проблему, вы можете снова изменить принципиальную схему или язык описания оборудования, чтобы улучшить конструкцию. После проектирования, например массового производства, вы можете напрямую копировать другие чипы CPLD, то есть писать код. Если вы хотите выполнить другие проекты на чипе, например, проект светофора, вам придется снова нарисовать принципиальную схему или написать язык описания оборудования и повторить описанный выше рабочий процесс для завершения проекта. Эта модификация проекта эквивалентна косметическому ремонту дома, и для CPLD этот ремонт можно выполнять десятки тысяч раз.

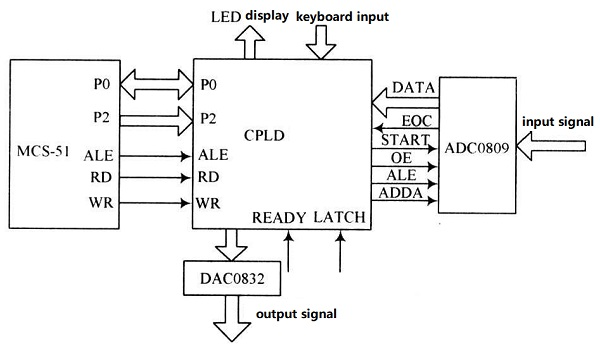

Схема системного интерфейса с использованием чипа CPLD

Члены семьи

После десятилетий разработок многие компании разработали программируемые логические устройства CPLD. Наиболее типичными являются продукты Altera, Lattice и Xilinx — трех самых авторитетных компаний мира. Часто используемые чипы приведены здесь:

Альтера EPM7128S (PLCC84)

Решетка LC4128V (TQFP100)

Ксилинкс XC95108 (PLCC84)

Ⅱ Состав CPLD

CPLD состоит из трех основных компонентов: логического блока , программируемого межсетевого канала и блока ввода-вывода .

Логический блок в CPLD похож на небольшой PLD. Обычно логический блок содержит от 4 до 20 макроячеек, каждая из которых обычно состоит из массива терминов продукта, назначения терминов продукта и программируемых регистров. Каждая макроячейка имеет несколько конфигураций, и каждая макроячейка может использоваться в каскаде, что позволяет реализовать более сложную комбинационную логику и функции временной логики. Для высокоинтегрированных CPLD обычно предоставляются встроенные блоки массивов со встроенным ОЗУ/ПЗУ.

Программируемые каналы межсоединений обеспечивают сети взаимосвязей между логическими блоками, макроячейками и контактами ввода/вывода. Блоки ввода/вывода (блоки ввода/вывода) обеспечивают интерфейс между внутренней логикой и выводами ввода/вывода устройства.

Состав CPLD

CPLD с более крупными логическими масштабами обычно также имеют встроенную схему тестирования границ JTAG, которая позволяет проводить комплексное и тщательное системное тестирование запрограммированных программируемых логических устройств высокой плотности в дополнение к внутрисистемному программированию через интерфейс JTAG.

Из-за различных процессов интеграции, масштаба интеграции и производителей существуют также серьезные различия в структуре разделов и логических ячейках различных CPLD.

Ⅲ Структура CPLD

Устройство EPM7128S

(1) Базовая структура устройства EPM7128S

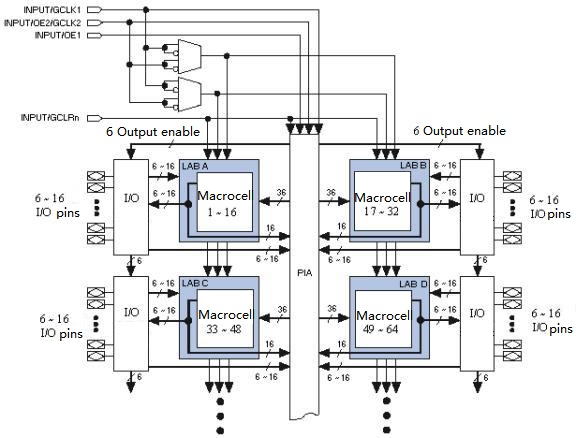

Устройство EPM7128S в основном состоит из блока логической матрицы LAB, макроячейки, блока управления вводом/выводом и программируемой матрицы межсоединений PIA.

В многоматрицной матричной структуре каждая макроячейка имеет программируемую матрицу и фиксированную или матрицу, а также конфигурируемый триггер с независимо программируемыми функциями тактового сигнала, включения тактового сигнала, сброса и сброса. Несколько LAB соединены через программируемую межсетевую матрицу PIA и глобальную шину. Каждая LAB также подключена к соответствующему модулю управления вводом/выводом для обеспечения прямых каналов ввода и вывода.

(2) Структура макроячеек EPM7128S

Каждую макроячейку EPM7128S можно индивидуально сконфигурировать для работы с комбинационной или временной логикой. Макроячейка состоит из трех основных частей: логической матрицы, матрицы выбора членов произведения и программируемых регистров. Программируемые регистры можно запрограммировать для обхода и реализации комбинационной логики в соответствии с логическими потребностями. При использовании в качестве регистров соответствующее программное обеспечение для разработки устройств с программируемой логикой выберет эффективную работу регистра в соответствии с потребностями логики проектирования, чтобы минимизировать ресурсы устройства, используемые для проектирования.

Устройство XCR3064XL

Структура макроячеек устройства XCR3064XL состоит из функциональных блоков и ячеек ввода-вывода, соединенных массивами межсоединений с нулевым энергопотреблением, при этом каждый логический блок содержит 16 макроячеек.

Ⅳ Идентификация и классификация FPGA и CPLD.

Идентификация и классификация FPGA и CPLD в основном основаны на их структурных характеристиках и принципах работы.

Обычными методами классификации являются:

Устройства, которые структурированы в соответствии с терминами продукта для формирования логического поведения, называются CPLD, например, серия ispLSI от Lattice, серия XC9500 от Xilinx, серия MAX7000S от Altera и серия Mach от Lattice (ранее Vantis).

Устройства, структурированные по методу справочной таблицы для формирования логического поведения, называются FPGA, например, серия SPARTAN от Xilinx, серия FLEX10K или ACEX1K от Altera и т. д.

Хотя FPGA и CPLD являются программируемыми ASIC-устройствами и имеют много общих черт, они имеют свои особенности из-за различий в структуре CPLD и FPGA:

① CPLD больше подходит для реализации различных алгоритмов и комбинационной логики, а FPGA больше подходит для реализации логики синхронизации. Другими словами, FPGA больше подходит для структур с большим количеством триггеров, а CPLD больше подходит для структур с ограниченным количеством триггеров и богатым набором продуктов.

②Непрерывная структура проводки CPLD определяет, что ее временные задержки являются равномерными и предсказуемыми, тогда как сегментированная структура проводки FPGA определяет непредсказуемость ее задержек.

CPLD программируется путем изменения логической функции с фиксированной схемой соединения, а FPGA программируется путем изменения разводки внутренних проводов; FPGA может быть запрограммирована под логическим вентилем, а CPLD — под логическим блоком.

④FPGA более интегрированы, чем CPLD, и имеют более сложную структуру подключения и логическую реализацию.

⑤ CPLD удобнее использовать, чем FPGA. CPLD программируется по технологии E2PROM или FASTFLASH, внешняя микросхема памяти не требуется, проста в использовании. Хотя информацию о программировании FPGA необходимо хранить во внешней памяти, используются сложные методы.

(6) CPLD работают быстрее, чем FPGA, и имеют большую предсказуемость времени. Это связано с тем, что FPGA программируются на уровне вентилей и используют распределенные взаимосвязи между CLB, тогда как CPLD программируются на уровне логических блоков и их взаимосвязи между логическими блоками являются коллективными.

CPLD в основном основан на программировании E2PROM или флэш-памяти, которую можно программировать до 10 000 раз, и она имеет то преимущество, что информация о программировании не теряется даже при выключении системы.

CPLD можно разделить еще на две категории: программирование на программаторе и программирование в системе. FPGA в основном основана на программировании SRAM, и информация о программировании теряется при выключении системы, и каждый раз, когда устройство включается, данные программирования необходимо перезаписывать извне устройства в SRAM. Данные программирования необходимо перезаписывать в SRAM снаружи устройства каждый раз при его включении. Преимущество в том, что его можно программировать любое количество раз и можно быстро запрограммировать в работе, таким образом достигается динамическая конфигурация на уровне платы и на уровне системы.

⑧ Конфиденциальность CPLD хорошая, конфиденциальность FPGA плохая.

⑨ Как правило, энергопотребление CPLD больше, чем у FPGA, и чем выше уровень интеграции, тем это более очевидно.

Frequently Asked Questions